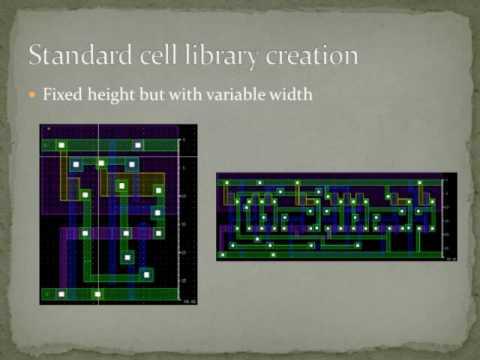

Standard cell library

Introduction

Standardcelllibrary,includinglayoutlibrary,symbollibrary,circuitlogiclibrary,etc.Containscombinationallogic,sequentiallogic,functionalunitsandspecialtypesofunits.Itisafundamentalpartoftheback-enddesignprocessofintegratedcircuitchips.Theuseofpre-designedandoptimizedlibraryunitsforautomaticlogicsynthesisandlayoutlayoutcangreatlyimprovedesignefficiencyandspeedupthetimeforproductstoenterthemarket.

Therefore,powerfulintegratedcircuitdesigncompaniesandprocessingmanufacturersshouldhavetheirownstandardcelllibrary,andestablishacompletesetofcorrespondingprocesslines,richcontent,reasonabledesignandcorrectparametersThecelllibraryhasbecomeanecessaryconditionfordesign.

Typesofstandardunits

FromFigure1,wecanroughlyunderstandthetypesofstandardunits.Generallyspeaking,variousgatecircuits,flip-flopsandvariousI/Ounitsarethenecessaryconfigurationsforastandardcelllibrary.TheseconfigurationscanmeetthedesignneedsofapuredigitalcircuitASICcircuit.Othermacrocells(includinganalogmacrocells)ManyprocesslinesareoftenprovidedasIP,sotheymaynotbefullyincludedinthestandardcelllibrary.

Figure1Typesofcelllibraries

a)Standardcells

Standardcellsincludeinverters,ANDgates,registers,selectors,fulladders,etc.Abasicunit,eachstandardunitcorrespondstomultipleunitcircuitswithdifferentsizes(W/L)anddifferentdrivecapabilities,andthecircuitswithdifferentdrivestrengthsareallintegralmultiplesofthebasicsizeortheminimumsize.Thediversityofthecelllibrarycaneffectivelyimprovetheefficiencyofsynthesistoolsandautomaticplacementandroutingtools,andalsoallowsdesignerstomorefreelyoptimizebetweenperformance,area,powerconsumptionandcost.

Inordertorealizetheautomaticplacementandroutingofthetool,therearemanyspecialdesignrulesinthestandardcelllayoutdesignwhenbuildingthelibrary,whichisroughlyasfollows:

AllcellsTheyareallequalrectangles,ortheheightisanintegermultipleofthebasicheight,toensurethatotherunconventionaldimensionsarenotusedinthecircuitdesignstage.

InordertoensurethateachunitdoesnotcauseDRCerrorswhenplacedwithotherunits,alllayoutsshouldbedesignedwithapredefinedtemplate.

Sincetheclassicrouteradoptsagrid-basedmethodforwiringconnection,thismethodcansimplifythealgorithmofthewiringtoolandreducethememoryresourcesoccupiedbythecomputer.Therefore,theposition,size,andshapeoftheinputandoutputportsofallunitsareasfaraspossibletomeettherequirementsofthegridspacingtoimprovetheefficiencyoftherouter.

PowercordandgroundwireGenerallylocatedattheupperandlowerboundariesoftheunittofacilitateconnectionsharingandreducechiparea.

b)Moduleunit

Moduleunit(block)includesdigitalmodulesofvarioussizes:RAM,ROM,COT,IP,voltagecomparatorAndsoon,alsoincludesanalogmodules:operationalamplifiers,ADC/DAC,phase-lockedloops,oscillators,etc.

Thelayoutofthemoduleunitanditsphysicallibraryconstructionaresimilartothoseofthestandardunit.ForbuildingalibraryofRAMorROMmoduleunits,youcanimitatetheprocessofstandardunits,firstbuildRAMorROMbasicunits,andthenuseasemi-automaticmethodtobuildthelayoutfrombottomtotopaccordingtothebitlengthandwordlength.Fordigitalmoduleswithspecialrequirements,suchasIPandCOTmodules,thelayoutiscreatedthroughafullycustomizedmethodforlibrarybuilding.

c)I/Ounit

TheinterfacecircuitforcommunicationbetweenthechipandtheprintedcircuitboardiscollectivelycalledtheI/Ocircuit.Astheinterfacebetweenthechipandtheoutsideworld,itmusthavealargedrivecapability,theabilitytoresistelectrostaticdischarge,theabilitytoresistnoiseinterference,andsufficientbandwidthandover-voltageprotection.ThetypesofI/Oincludeinput1/0,outputI/O,bidirectionalinputandoutputI/O,powersupplyI/OandgroundingI/O.ThecompositionofI/Ocanberoughlydividedintothreeparts,namelyPADinterface,signalbuffercircuitandelectrostaticdischargeprotectioncircuitESD.

Applicationofstandardcells

Standardcellscanusuallybeusedinthesynthesisandlayoutstagesofdigitalcircuitdesign.

Intheuseoflayout-levelnetlistsandcell-levellibrarylayouts,wiringtoolscanaddsignalconnectionlinesandpowerlines.

Purpose

Thestandardcelllibraryisusedtoprovidesupportforlogicsynthesisandplacementandroutingtools.ThefollowingdocumentsareexportedforuseSupport:

GDSIIfile:containsthelayoutinformationoftheunit,usedtosynthesizethefinalfullchiplayout;

LEFfile:ThisfileisusedforlayoutandroutingintheSOCENCOUNTERenvironmentThisfileprovidesprocessinformationandgeometriccharacteristicsofeachunitfortheplaceandroutetool;

Timingfile:ThetimingfileisusedforDesignComplierandotherdigitalsynthesistoolsforgate-levelsynthesis,andisusedforSOCENCOUNTERAndotherplaceandroutetoolsfortimingoptimizationandadjustment.

Circuitlogicandsymbollibrary:usedforlarge-scalechipcircuitdesign.

Designprocess

Thedesignofthestandardcelllibrarymainlyincludestheextractionofcircuitdesignandlayoutdesignmemoryfiles.Amongthem,thecircuitdesignlinkmustdeterminethedeterminationofthelibrarycapacityandtheoptimizationofthetimingcurve.Inthisdesign,therequiredcelltypeanddrivingcapabilitymustbefinallydetermined.Afterthecircuitdesigniscompleted,thelayoutdesignisoftencarriedoutthroughafullycustomizedmanualdesign..However,therearealsosomeautomatedtools,suchasCELLERITYandCLIP.

Latest: Shen Kuo

Next: Learning behavior