QBM

Introduction

QBM (Quad Band Memory) adopts a "bit stuffing" mechanism, which does not require higher clock frequency memory components, and does not increase the memory benchmark Under the condition of frequency, QBM can use existing DDR memory and other components to achieve a configuration that can obtain twice the data rate. It is not a brand-new memory architecture, nor a brand-new memory product, but a memory control technology.

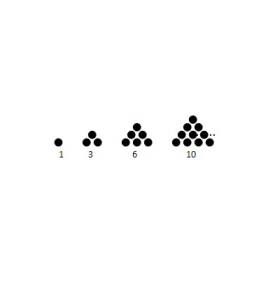

QBM, like DDR, improves the transmission bandwidth by shortening the clock cycle of data transmission, but there are differences between the two. DDR achieves bandwidth multiplication by accessing data on both the upper and lower edges of the clock frequency. QBM has made an improvement on this basis. A QBM module is composed of two DDR memory modules. One of the modules runs at a normal frequency, while the clock cycle of the other module is exactly 90 degrees slower than the previous module clock cycle, which means that the two work The start time differs by 1/4 clock cycle. Through this simple method, QBM can get twice the efficiency of DDR memory, that is, 4 data reads and writes are realized in one clock cycle. A FET chip is used to connect the two DDR modules of QBM, and this FET chip acts as a field effect tube-as a delay switch. This simply completes the series connection of two DDR modules.

Background

With the increase of CPU front-side bus bandwidth and the emergence of high-speed local buses, such as AGP8X, USB2.0, high-speed Ethernet, etc., memory bandwidth has become larger and larger in the system Bottleneck. Therefore, a variety of new memory solutions have emerged. The first thing to mention is DDR II. Japan’s ELPIDA has launched DDR II particles with a data transfer rate of 1000Mbps per pin. DDR II also has the advantages of low power consumption and high reliability. However, all major memory manufacturers believe that DDR II will not become the mainstream until at least 2004. A little bit pessimistic is that DDR II will become the mainstream in 2005.

The mainstream memory in 2003 was still DDR333, so for high-end desktop platforms and workstation platforms, what memory solutions will be adopted? On the server platform, Intel has launched the E7500 dual-channel DDR chipset, and will subsequently launch the E7502 for high-end desktop systems and workstations, which can use dual-pass DDR333 memory, and its memory bandwidth is even higher than that of the E7500 (limited to the front side bus of Pentium4Xeon Frequency, E7500 can only support DDR200 and DDR266 memory modules). VIA's dual-channel DDR chipset P4X600 has been sampled and is expected to be available soon. However, the cost of a dual-channel DDR system is higher. It requires six-layer PCB support. Two modules must be used at the same time, and the motherboard wiring is more complicated. Therefore, the positioning of the dual-channel DDR system will be relatively high, mainly for the workstation platform. . VIA also introduced a high-bandwidth memory technology, QBM, the name of QBM is not the first time I have heard it, but for the first time that mainstream memory manufacturers support it. QBM can be said to be a high bandwidth solution with backward compatibility and lower cost.

In order to meet the requirements of increasing processor data throughput, as well as the requirements of high-speed graphics local buses, disk channels, high-speed serial buses, and PCI devices, the memory architecture has been updated. Since the 486, memory has been one of the main bottlenecks restricting the development of system performance. Although the memory has developed from fast page memory to EDO memory and then to SDRAM memory, the memory can finally be synchronized with the system clock frequency at this time. The bit width of the memory bus has also developed from 32-bit to 64-bit, and the frequency has also been changed from 66MHz to 100MHz to 133MHz. The speed of the memory is constantly improving but it is always unable to keep up with the requirements of the platform. When SDRAM developed to a bottleneck, two different paths appeared. One was DDR SDRAM developed on the basis of SDRAM. It achieved the effect of frequency multiplication by twice the sampling rate in one clock cycle. The other is the serial memory bus RAMBUS. Because the frequency of the serial bus can be made very high, the current RDRAM uses 8bit Prefetch, which is much more advanced than DDR, so it is in a leading position in memory bandwidth. But with the development of the market, DDR began to become the mainstream, and the RDRAM market shrank to high-end workstations. During the development of SDRAM, there have been some other promising technologies. The most likely to succeed should be QDR, so the name Siyi QDR can transmit data four times in one clock cycle. The memory bandwidth is at the same frequency. DDR is twice, and QDR memory still uses DDR particles, QDR is also four times the data transfer rate. However, no mainstream chipset manufacturer supports QDR, but QBM has won the favor of VIA.

Principle

The QBM chipset simply uses a traditional 64-bit DDR SDRAM memory interface, which is then integrated into a memory controller that supports the QBM module. One of its modules requires a minimum of 16 DDR SDRAM particles, 8 of these particles form the first bank, and the other particles form the second bank. They occupy both sides of the DIMM respectively. The QBM module still uses the 184pin interface. Like the current DDR SDRAM module, the interface electrical specification is STTL_2, and the 2.5V operating voltage requires a bus termination resistor on the motherboard.

There are 8 registers (registers, QBM-10, respectively for 8 DDR SDRAM particles) on the QBM module. The functions of these registers are the same as the phase-locked loop (PLL) circuit. Through this phase-locked loop The circuit can delay the clock signal by 90 degrees. It delays the phase of the second bank's signal by 90 degrees, while the first bank still uses the original clock phase. The 8 registers also have the function of FET. The so-called FET is the switch of a circuit. In each clock cycle, two banks are cyclically switched to transmit signals. Because there is a 90-degree phase delay, four bits can be transmitted in one clock cycle. Data, that is to say, the final result is that two DDR data transfer rates can be obtained in each clock cycle, and each pin can transmit 4 bits of data per clock cycle. This is also the origin of the name of Quad Band Memory.

The QBM structure increases the data bandwidth of the memory subsystem without increasing the memory reference frequency (memory bus operating frequency). QBM uses existing DDR SDRAM and a "2 to 1" FET switch; a phase-locked loop (PLL) with a reference frequency output, a 90-degree phase shift output of the reference frequency, and a double reference frequency output to achieve 4 times The memory bandwidth (relative to SDRAM with the same reference frequency).

QBM makes use of the data on the receiver side (referring to the memory controller in the chipset) and it is not necessary to keep it valid for a long time. When the reference frequency is 100 MHz, the ideal hold time of the data bits output by each DDR device is 5 nanoseconds. When the receiver's setup and hold time is less than 1 nanosecond, a lot of time is wasted (the receiver waits for memory data). In order to reduce the bit time, it is necessary to increase the reference frequency. In order to avoid problems caused by high frequency, QBM divides each bit time so that another valid data bit is inserted into the time period not occupied by the previous data bit. Simply put, QBM is a "bit packing" mechanism. You can clearly see this "bit packing" mechanism in the timing diagram 1 below, which requires some improvements in the memory controller. QBM connects two DDR chips to a "2 to 1" FET switch. They have the same reference frequency, except that the clock of one of the devices has a 90 degree (or 1/4 cycle) phase shift, so it is transmitted to the receiver The data bits are twice the data bits produced by DDR. In one clock cycle, four bits are "stuffed", and QBM can reach twice the data transfer rate of DDR I.

History

The future is bright

On January 23-24, 2001, at the Platform Conference held in St. George, California, USA Memory Modules Manufacturer Kentron demonstrated QBM technology. Through this technology, 4 data transmissions can be realized in one clock cycle, and the current traditional DDR memory can be doubled in the data transmission bandwidth at the same operating frequency, which fundamentally solves the problem of DDR memory relative to RDRAM memory. Shortcomings, at the same time this technology can play the same role in any current DDR memory.

The cost of the FET module, an important component responsible for external control of the QBM operation, is extremely low. A FET module only costs about $1. With this FET module, in addition to achieving higher speeds with current DDR memory, it can also reduce system power consumption, increase memory density, and achieve faster system bus speeds. High performance at low cost. In other words, the cost of QBM memory can be well controlled, and its cost is theoretically similar to that of DDR memory.

In view of the good development prospects of QBM, although few memory manufacturers directly express their support for QBM technology, three well-known semiconductor companies, ST Micro Electronics, Integrated Circuit System and Actel, have already made public Indicates support for QBM technology. Kentron also publicly expressed its support, and is currently conducting detailed discussions with a number of companies, including VIA, the advocate of DDR memory architecture, and NVIDIA, the dominant graphics card industry that is stepping into the field of chipset research and development. At the same time, there are rumors about SiS, ALi and other chipset manufacturers and ATi intending to support QBM.

Infinite scenery

In August 2003, VIA demonstrated its latest Intel Pentium4 chipset PT880 at the QuakeCon game conference for the first time, and announced that the chipset will support dual-channel traditional DDR The memory will also support dual-channel QBM memory at the same time, making the chip attract attention for a while.

Public appearance

At the Compute x2004 exhibition, VIA publicly demonstrated its QBM memory for the first time, demonstrating the work of QBM memory on the p4 platform. The product on display seems to use a dual-channel working mode. The working frequency of QMB memory is 533MHz. It can be seen that the memory product was shipped on April 21, 2004, but it is still only an engineering sample.

Helplessly die

On November 12, 2004, VIA’s VIA Electronics Chip and Graphics Chip Business Deputy Director Xu Weidesheng first revealed to reporters that due to QBM’s lack of support from memory manufacturers, Coupled with the popularity of DDR2, QBM memory has no more room for survival. VIA's chipset will no longer support QBM memory, and the development of QBM memory has been terminated.

Latest: RDRAM memory

Next: Data bus width