Instruction decoding

CPU Operation principle

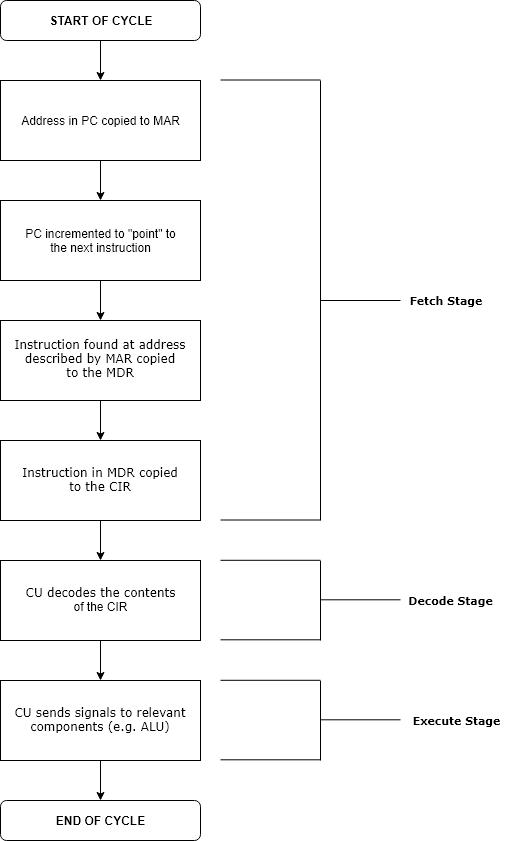

CPU's main operation principle, whether its appearance is performed, is executed in a series of instructions stored in the program. It is discussed here that a device that follows the universal architecture design. The program is stored in a computer memory in a series of numbers. Almost all of the CPU operation principle can be divided into four phases: fetch, decodes, executes, and writeback.

Retrieve instructions in the first phase, extraction, and a number of values (a series of values). The PROGRAM Counter specifies the location of the program, the program counter saves the value of the identification program. In other words, the program counter records the trail of the CPU in the program.

After extracting the instruction, the program counter increases the memory unit according to the length of the instruction. The extraction of the instructions often takes to relatively slow memory, resulting in the delivery of the CPU waiting instruction. This problem is primarily discussed and the tubing and pipeline architecture in modern processors (see below).

CPU determines its execution behavior based on instructions extracted from the memory. In the decoding phase, the instruction is disassembled as a meaningful piece. The value interpreted as an instruction based on the CPU's instruction set architecture (ISA) definition.

Part of the command value is an OPCode, indicating which of the operations you want. Other values are usually supplied to the necessary information, such as an additional operational target. Such an operation target may provide a constant value (ie, an immediate value), or a spatial address value: a tentative or memory address, based on the address mode.

In the old design, the instruction decoding portion in the CPU is a hardware device that cannot be changed. However, in many abstract and complex CPUs and instruction set architectures, a microprogram is often used to help the conversion instructions are signals for a variety of forms. These microprograms are often overwritten in the finished CPU, which is convenient to change the decoding instruction.

After the extraction and decoding phase, then enter the execution phase. In this stage, various CPU components that can perform the desired calculation can be connected.

For example, a additional operation, the calculation logic unit (ALU, ARITHMETIC LOGIC Unit) will be connected to a set of inputs and set outputs. The input provides the value to be added, and the output will contain the sum results. The ALU contains circuit systems to complete simple ordinary computing and logical operations (such as addition and bit element operations) in the output. If the addition operation produces an excessive result of the CPU process, in the Sign Speedic Overflow flag, the arithmetic overflow may be set (see the numerical accuracy discussion below).

final phase, writing back, and writing the results of the execution phase in a certain format. The calculation results are often written to the provisions inside the CPU for quick access to the instructions. In other cases, the calculation results may be slow, but the capacity is large and a cheaper main memory. Some types of instructions will operate program counters without directly generating results. These are generally referred to as "jumps" and bring cycle behavior in the program, and conditional execution (through conditional jump) and a function.

Many instructions also change the status bit of the flag scalar. These markers can be used to affect program behavior, because they often show various computational results.

, for example, determines the size of the two values in accordance with a "comparison" instruction, set a value on the flag schematic according to the comparison result. This logo can determine the program trend by subsequent jump instructions.

After executing instructions and writes the result data, the value of the program counter is incremented, reversed the entire process, the next instruction cycle is normal, and the next order command is extracted. If the jump instruction is completed, the program counter will modify the command order that jumps to, and the program continues to be normal. Many complex CPUs can extract multiple instructions, decodes, and execute at the same time. This part generally involves the "classic RISC line", which actually popular in many electronic devices that use simple CPUs (often referred to as microControllers).

Latest: Propagation mode